优化下一代互联网基础架构系统中的差分晶体振荡器抖动性能

为了在实际应用中实现Si534x差分晶振的100fs抖动性能,设计人员应该考虑一些简单的准则以最小化串扰并优化整体抖动性能.这些准则适用于任何高速时钟晶体振荡器的频率合成.

每当许多高频,快速上升时间,大振幅信号彼此接近时,都会有一些它们之间的串扰量.Si534x系列差分有源晶振的抖动如此之低,以至于以前的串扰相对较小最终测得的输出抖动的重要部分.来源某些串扰是由于Si534x器件和一些将由PCB引入.很难分配两个源之间的抖动部分,因为抖动只能将Si534x晶振安装在PCB上时进行测量.本应用笔记提供了简单的准则,使设计人员能够优化抖动性能.

一、最佳抖动性能的四个简单规则

1.1选择差分晶振的差分输出选项(LVDS,LVPECL,HCSL)

差分输出产生平衡的互补输出信号,旨在产生最佳的抖动性能.这些差异信号格式还固有地产生最小的共模噪声(最小化EMI),并且它们通常消耗的功率比CMOS格式.

1.2仔细订购差分输出晶体振荡器

减少串扰的最简单方法之一是安排时钟输出,这样,彼此之间更可能遭受串扰的时钟实际上就不会彼此相邻放置.对于网络应用,抖动集成带宽通常来自对终端系统很重要的相关通信标准.集成频带之外的抖动被认为不是问题.集成带的详细信息因应用程序和标准而异.SONETOC-48常用的默认集成频带为12kHz至20MHz,在以下示例中使用:

如果两个相邻的时钟石英晶体振荡器输出彼此之间的距离小于20MHz(抖动积分频带的范围),则可能存在串扰问题.考虑在156.25MHz晶振输出之后紧随155.52MHz晶振输出的示例.自156.25MHz–155.5222MHz=730kHz,则两者之间的混合差异将很好地位于12kHz至20MHz的抖动屏蔽频带内.因此,设计师应避免在156.25MHz差分晶振旁边放置155.52MHz差分晶振.

请注意,此积分带宽接近度放置准则不适用于彼此简单整数倍的差分晶体振荡器.例如,因为125MHz*5=625MHz,所以可以在625MHz差分振荡器旁边放置125MHz差分晶振.简单整数关系表示一个差分晶振的边缘不会相对于另一个差分晶振的边缘移动.

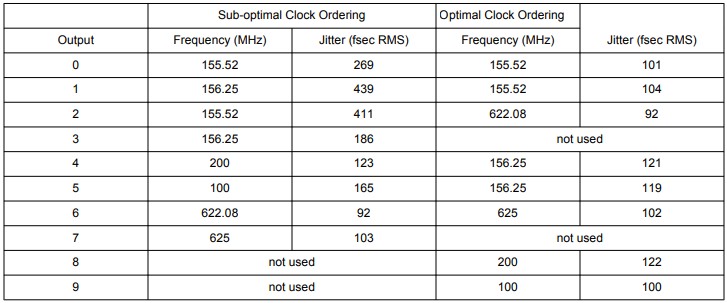

1.3具有未使用输出的独立差分晶体振荡器

未使用的差分晶振输出可用于物理上分开时钟,否则会相互干扰.例如,如果有未使用的晶振输出,可以将其放置在155.52MHz和156.25MHz晶振之间以物理上将它们分开.表1所示重新排列使用的晶振并有策略地放置未使用的晶振以改善抖动的好处.在这个例子中,十使用两种不同的方式对输出Si5345贴片晶振进行了编程:一种忽略重新安排晶体振荡器输出的建议,另一种忽略考虑到它们.集成了12kHz至20MHz的抖动,所有输出均为2.5V的LVDS.显然,重新排列输出降低了抖动,并在所有输出上实现了高性能.

表1.1.输出时钟排序对抖动性能的影响

1.4避免在关键抖动应用中使用CMOS输出格式

•因为CMOS输出晶体振荡器在轨到轨之间摆动并且不平衡(与LVPECL,LVDS,CML和HCSL),CMOS输出在所有晶振沿都会产生明显的电流浪涌,因此是主要的串扰干扰源.对于因此,对于抖动敏感的应用,应尽可能避免使用CMOS输出.

•当必须使用CMOS格式时,应“隔离”CMOS石英晶体振荡器,并使其与非相同的频率.

•在Clock Builder Pro中选择“互补”输出选项(而不是同相选项)以帮助平衡输出电流过渡期间的浪涌.

•如果未使用CMOS对的输出侧之一,但正在主动切换,则不要终止负载.

•考虑对CMOS晶体振荡器使用外部低抖动差分模式,将缓冲器远离PCB上的Si534x晶振,以避免耦合.

二、马刺,抖动积分带和谐波

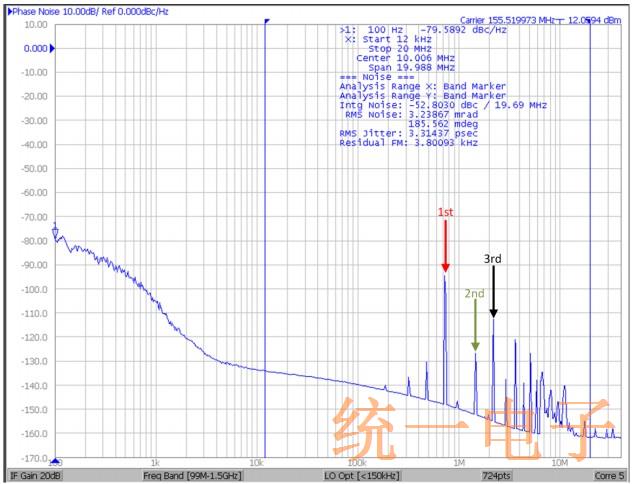

当附近的晶振输出耦合到输出晶振时,抖动性能会下降.例如,假设155.52MHz差分晶振输出位于156.25MHz差分晶振输出旁边.两者之间的频率差为156.25MHz–155.52MHz=730千赫.结果,在155.52MHz载波旁有一个730kHz处的杂散,对应于标记为在图1中为“1st”.正如CMOS输出晶体振荡器产生的方波所预期的那样,二次谐波明显较小,它位于距离载波2*730kHz=1.46MHz的位置,并标记为“第二”.三次谐波大于二次谐波,但不大于和第一个一样大.它位于3*730kHz=2.19MHz,标记为“3rd”.因为所有这些与其他谐波相关杂散位于12kHz至20MHz抖动积分频带内,它们都可能有助于降低抖动性能(如图所示).在表1中)为差分输出有源晶振.这种降级的幅度(CMOS时可能为数百飞秒时钟与其他CMOS时钟耦合)取决于许多因素,其中包括I/O电压,信号格式和PCB布局.

图2.1.CMOS至CMOS输出的杂散和谐波示例

三、结论

通过遵循本应用笔记中的基本准则,设计人员可以使用Si534x差分晶振抖动实现100fs级的抖动性能.对于要求这种抖动性能水平的晶体振荡器,设计人员应:

•为所有对抖动敏感的晶振选择差分格式.

•仔细订购晶体振荡器输出(根据频率和集成带宽的接近度).

•通过在输出之间放置未使用的输出来分离耦合敏感.

•仅对抖动性能不是至关重要的晶体振荡器选择CMOS格式.

微信号

微信号