任意频率的Si51x晶体振荡器多项输出介绍

任意频率的Si51x晶体振荡器多项输出介绍

1.简介

本应用笔记提供了将输出时钟信号连接到Si51x系列的端接建议XO振荡器和VCXOIC的型号,不适用于任何其他Silicon Laboratories器件.

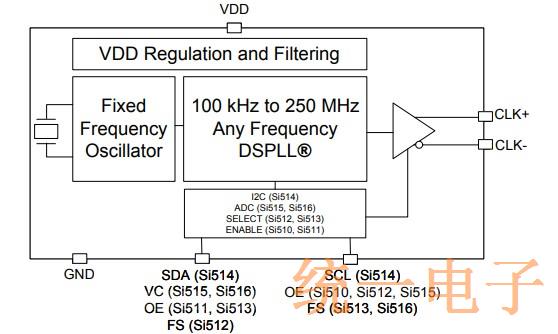

Si51x系列任意频率XO,VCXO大大简化了当今许多XO之间的接口连接任务常见的信号类型.输出与单端CMOS或差分信号(LVPECL,LVDS,HCSL)并支持多种电压电平(3.3、2.5或1.8V).这些设备的框图如图1所示.

Si510和Si511是具有输出使能的单频XO.Si512和Si513是双频具有输出使能的XO振荡器.Si514是使用I2C控制的频率可编程设备.Si515和Si516具有输出使能(Si515)或双频(Si516)的VCXO.

图1.Si51x器件框图

注意:CLK-为单端CMOS输出格式的非连接状态.请参阅订购信息.CMOS格式限制为100kHz至212.5MHz.

2.输出

可以订购Si51x器件以提供差分或单端(CMOS)输出.什么时候配置为差分CMOS时,晶体振荡器生成两个信号,可以将其配置为同相或补充.输出格式由订购的零件类型决定,可以是以下信号之一类型:CMOS,LVPECL,LVDS和HCSL(请参见晶振的数据手册).

2.1.CMOS输出

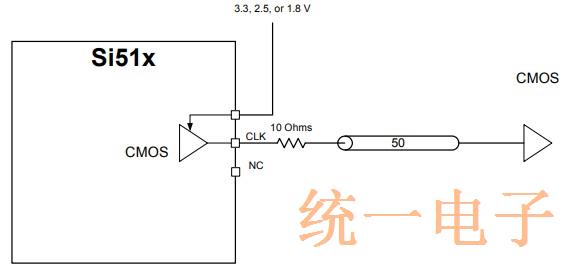

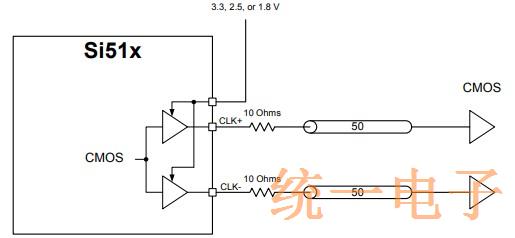

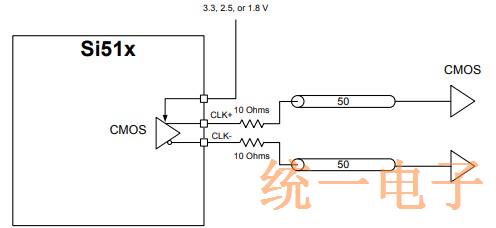

CMOS输出贴片晶振的输出阻抗约为40.因此,外部的Rs串联电阻为10为具有50迹线的电路板提供了最佳的端接,如图2所示(单输出),图3(双输出-同相)和图4(双输出-互补).如果板走线阻抗为高于50,Rs的值应为10加上电路板走线之差阻抗和50.图5,图6和图7显示了具有单相,双同相和双相的示波器波形互补CMOS输出.

图2.与CMOS接收器接口—单路输出

图3.与CMOS接收器接口—双输出同相

图4.与CMOS接收器接口—双输出互补

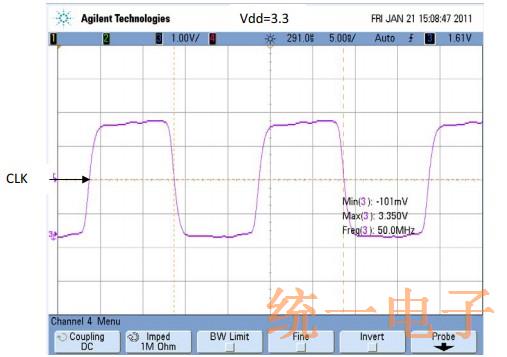

图5.CMOS输出系列以10Ω-单路输出端接

图6.CMOS输出系列以10Ω双输出同相端接

图7.以10Ω端接的CMOS输出系列-双路输出互补

2.2.LVPECL输出

LVPECL输出石英晶体振荡器可以订购为3.3或2.5V标准LVPECL模式.输出器件可以交流耦合或直流耦合到接收器.

2.2.1.直流耦合LVPECL输出

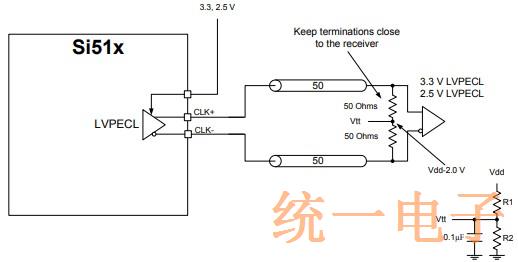

标准LVPECL振荡器支持两种常用的直流耦合配置.这两个都显示在图8和图9.LVPECL驱动器设计为以50Ω端接至VDD-2V,如图所示VTT可以配备一个简单的分压器,如图8所示.

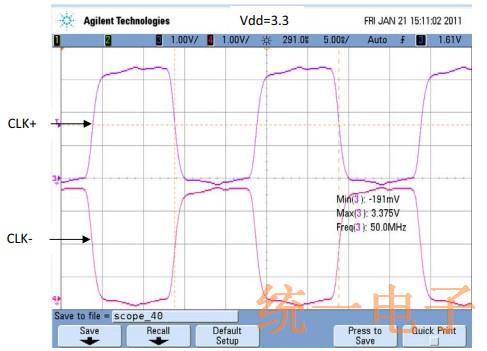

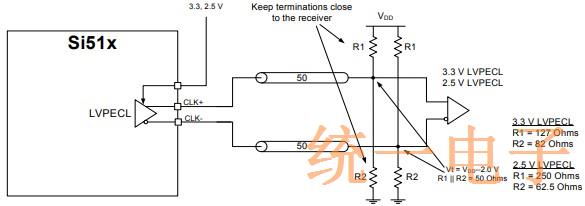

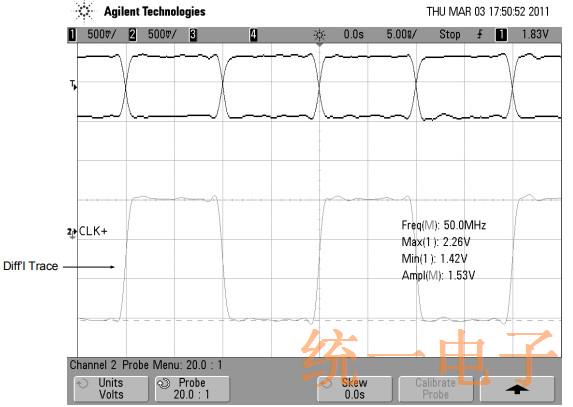

图9显示了另一种终止LVPECL的方法,该方法与戴维南等效.图8中的端接.它提供50的负载端接至VDD–2.0V.对于3.3V LVPECL,请使用R1=127并R2=82.5;对于2.5V LVPECL,使用R1=250和R2=62.5.这种类型的唯一缺点终止是戴维南电路消耗了VDD电源的额外功率.图10显示了一个范围3.3V LVPECL波形使用戴维宁等效终端输出50DC耦合至VDD–2.0V.

图8.与LVPECL的接口—DC耦合至50VDD至2.0V

图9.与LVPECL的接口—DC与戴维宁端接耦合

图10.LVPECL输出与戴维南等效终端直流耦合

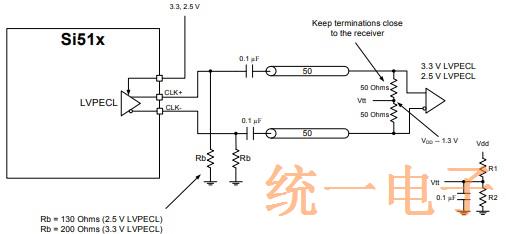

2.2.2.交流耦合LVPECL输出

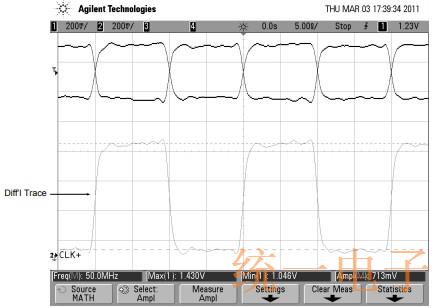

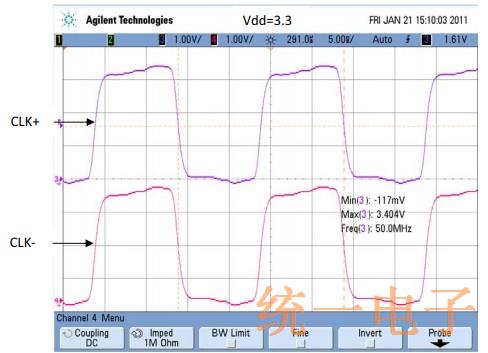

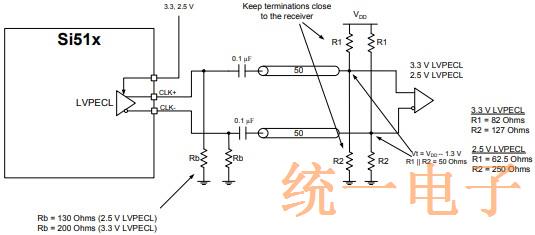

当接收器和驱动器具有兼容的电压摆幅但不同的公共端时,必须进行交流耦合模式电压.交流耦合适用于直流平衡信号,例如占空比为50%的时钟.图11描述了两种交流耦合标准LVPECL差分晶体振荡器的方法.戴维宁端接如图11所示当没有VBB(VDD–1.3V)电源时,这是一种方便且通用的方法;但是,它确实消耗额外的力量.图12所示的端接方法消耗的功率更少.VBB电源可以是由一个简单的分压器电路产生,如图12所示.图13显示了一个示波器波形,其中3.3VLVPECL使用戴维宁等效终端输出50Ω交流耦合至VDD–1.3V.

图11.与LVPECL的接口—AC与戴维宁端接耦合

图12.与LVPECL的接口—交流耦合并带有100端接

图13.LVPECL输出与戴维宁等效端进行交流耦合

2.3.LVDS输出

LVDS输出选件提供了一个非常简单且省电的接口,在使用时无需外部偏置连接到LVDS有源晶体振荡器.LVDS振荡器可以直流耦合或交流耦合到接收器.

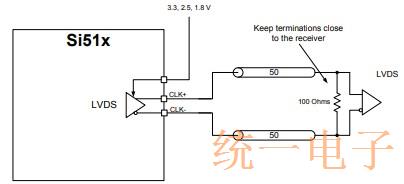

2.3.1.直流耦合LVDS输出

当使用3.3或2.5V电源电压时,Si51x提供标准的LVDS输出电平.虽然LVDS标准未指定1.8V电源电压,Si51x的特征是使用1.8V电源.图14显示了直流耦合的LVDS端接方案和图15示出输出直流耦合与LVDS的范围的波形.

图14.与LVDS的接口—DC与100差分终端耦合

图15.LVDS输出直流耦合

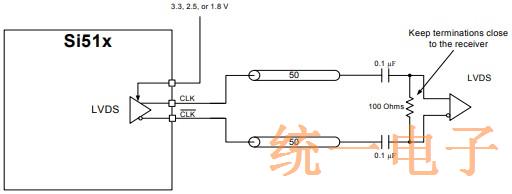

2.3.2.交流耦合的LVDS输出

Si51x LVDS输出可驱动交流耦合负载.交流耦合电容器可以放置在驱动器或接收器端,只要它们位于100终端电阻之前即可.保持100终端电阻应尽可能靠近接收器,如图16所示.

图16.与LVDS的接口-交流耦合

2.4.HCSL输出

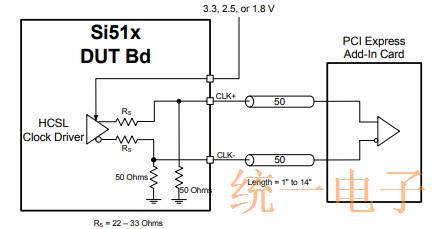

高速电流控制逻辑(HCSL)输出通常用于PCIExpress应用中.有需要不同端接方案的三种配置.第一种方案适用于驾驶员和负载位于不同的板上,称为“附加卡”配置.为了提供适当的在有或没有插入插件的情况下进行端接,在附近添加串联和并联电阻驱动器,如图17所示.由于附加卡接收器会给驱动器带来高阻抗负载.传输线,线的特征阻抗与负载之间的阻抗不匹配引起反思.有源晶振器件的设计应使反射或回铃声至少提供从0V的差分中点开始有±100mV的裕量.图18显示了Si51x HCSL驱动器的输出波形(在接收器的输入端测量)并显示驱动12英寸传输时的回铃电压裕度线使用33串联电阻.

图17.将Si51x连接到HCSL接收器—“外接卡”配置终止

图18.HCSL输出—“Rs=33,L=12英寸”的“附加卡”配置

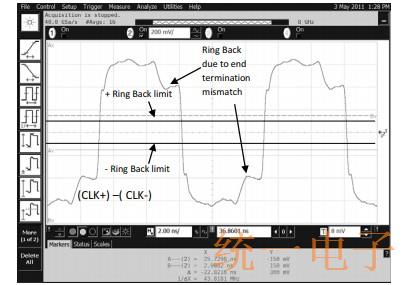

第二个HCSL配置也是“附加卡”配置,没有任何外部端接,如图所示如图19所示.此配置利用了驱动器的内部端接来消除任何外部组件.没有外部终端,HCSL输出的单端幅度约为600mV或约为1.2V环回反射之间的差分幅度,远远超出了所需的±100mV环回限制.图20显示Si51x HCSL晶体振荡器的输出波形(在接收器的输入端测量),并显示Ring Bank仅使用内部终端驱动12英寸传输线时的最大电压裕量.

图19.将Si51x连接到HCSL接收器-“外接卡”配置终止

图20.HCSL输出—具有内部终端的“附加卡”配置

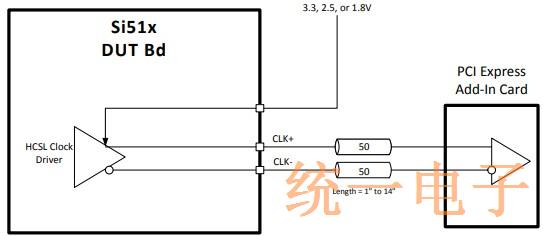

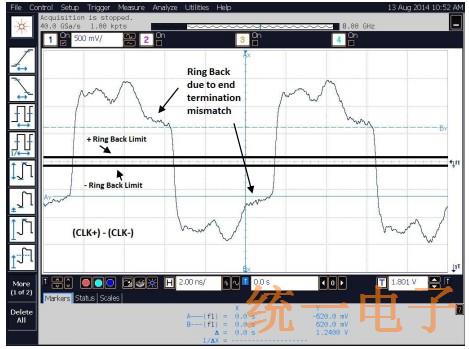

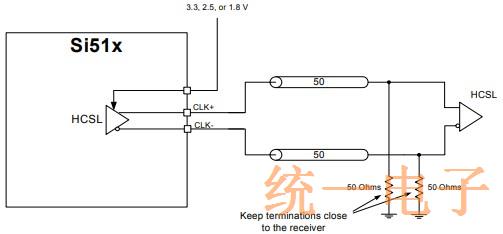

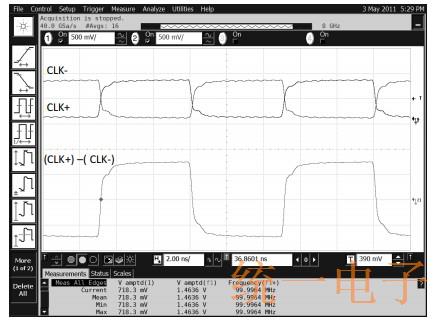

第三种HCSL配置是当时钟晶体振荡器和负载位于同一块板上时,称为“同一板”配置.在这种情况下,传输线的输入端应使用50欧姆的电阻端接.时钟接收器,如图21所示.图22显示了HCSL驱动器的输出波形.配置(在接收方测量).

图21.将Si51x连接到HCSL接收器—“同一板”配置

图22.HCSL输出—“同一板”配置

微信号

微信号